会议动态

CCF-DAC挑战赛ASIC DRC违例预测模型设计及AI-PC部署挑战挑战赛

1. 赛题背景:

随着人工智能和大数据应用的不断发展,对于高性能、低功耗的ASIC(专用集成电路)芯片需求日益增长。然而,设计和验证ASIC芯片的过程中,面临着一个重要的挑战:设计规则检查(DRC)违例的预测和解决。DRC是芯片设计流程中的关键步骤之一,用于确保芯片布局和连线满足制造工艺的要求。DRC规则由芯片制造工艺厂商提供,通常包括关于金属线间距、晶体管尺寸等方面的规定。设计人员必须确保他们的设计不会违反这些规则,否则可能导致芯片生产失败或性能下降。

传统上,DRC是在设计完成后进行的,但随着芯片规模的不断增大和制造工艺的不断进步,DRC的复杂度也呈指数级增长。这导致了设计验证周期的延长和生产成本的增加。因此,提前识别可能的DRC违例并及时进行修复变得至关重要。AI在解决这一挑战中发挥了重要作用。通过利用大量历史设计数据和对应的DRC结果,可以训练AI模型来预测新设计中可能出现的DRC违例。这种方法可以大大加速设计验证过程,降低成本,并提高芯片的生产质量。

本次赛题旨在促进AI在ASIC EDA算法领域的应用,同时探索EDA算法在AI-PC平台的异构计算部署,进而提升EDA算法在AI-PC上的计算效率。

2. 赛题综述

在本赛题中,参赛者将深入研究集成电路设计自动化中的一个关键挑战:DRC(设计规则检查)违例预测。这项预测任务的目标是根据ASIC芯片的布局信息,预测完成布线后可能出现的DRC违例位置。其主要工作步骤包括:(1)提取关键特征,(2)训练DRC违例模型,(3)将模型部署至AI-PC平台。

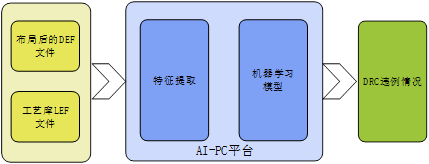

图1 本赛题的输入输出流程图

本赛题的输入文件包括布局后的DEF文件和工艺库LEF文件。参赛者需要根据这些文件进行电路网表抽取,获取ASIC设计的连接关系和单元类型,并提取出能够反映DRC违例的关键特征。然后,使用AI构建模型,并完成DRC违例的预测。

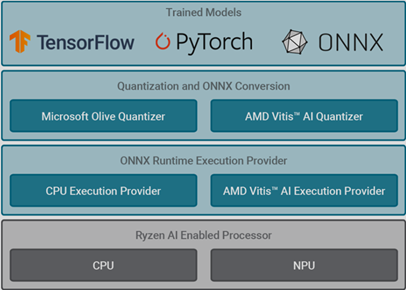

另外,为了应用NPU加速EDA流程,突出本赛题AI-PC主旨。参赛者需要根据算法的并行性和数据依赖性等特点,将算法的不同部分部署到AI-PC平台(AMD R9-7940)的CPU、核显GPU和NPU上进行计算加速。可以利用ONNX RUNTIME推理框架完成计算硬件的任务划分和调度,以发挥不同硬件的优势,从而最大化整个系统的计算效率和性能。

2.1关键特征提取

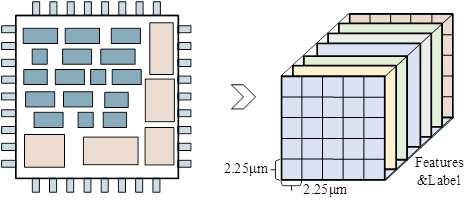

图2 版图切分及特征提取示意图

本次赛题使用的数据集是来自CircuitNet[1]数据集中的CircuitNet-N28。其布局后DEF位于CircuitNet/CircuitNet-N28/raw_data/LEF&DEF/ place-DEF,LEF文件为CircuitNet/CircuitNet-N28/raw_data/LEF&DEF/circuitnet.lef。在该数据集中,每个设计的芯片版图被划分为由2.25μm×2.25μm小块(tile)构成的二维数据。因此,参赛者需要对每个tile进行特征提取。在CircuitNet的介绍中已经提供了部分特征的提取方法,参赛者可以进一步改进相关特征和引入新的关键特征,从而实现更高的预测准确率。

此外,该数据集已经提供每个tile的DRC标签信息,其标签路径为CircuitNet/CircuitNet-N28/routability_features/DRC/DRC_all.tar.gz,参赛者可参考CircuitNet教程中的方法获取每个tile的对应的具体DRC违例数量。值得注意的是,本赛题的预测目标为该tile是否发生DRC违例,需要将标签处理为0——不发生违例,1——发生DRC违例,因此本赛题为二分类的预测任务,参赛者需根据该任务指定合适的目标函数。

2.2训练DRC违例模型

基于提取的关键特征和DRC违例标签,生成数据集,用于指导AI模型训练,参赛者可以参考RouteNet[2]和PGNN[3]的方法,构建合适的网络模型使用DRC的违例预测。参赛者也可以构建更合适的AI模型进行预测。

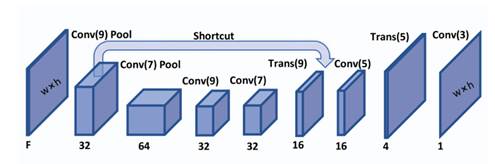

图3 RouteNet[2]的网络框架

值得注意的是,DRC违例模型构建完成后,参赛者可以选择合适平台上完成模型训练,但提交时,模型需部署在AI-PC上。

2.3模型迁移

AMD Ryzen™ AI 软件栈[4]提供了模型量化和执行提供者等驱动和工具,使开发者能够充分利用AI-PC上不同的硬件完成高效计算。参赛者可将不同深度学习框架下的模型转为onnx通用格式,然后采用ONNX Runtime推理框架完成模型的部署。在此过程中,参赛者可根据算法特点有机地将算法分配到CPU、核显GPU和NPU上执行,从而最大化计算效率。

3. 测试平台

比赛限定AIPC CPU型号为AMD R9-7940、内存大小为32G,使用windows

操作系统。请根据以上硬件和软件环境进行代码编写和优化,确保作品在指定

平台上能够顺利运行并发挥最佳性能。

4. 提交要求

windows执行码,设计文档,包括架构,算法,测试报告。其中windows执行码的命令行和参数要求如下。

DrcVioPrediction -def xxx -lef xxx -out xxx.csv |

输入文件为ASIC芯片布局后的def文件,及对应的工艺库文件lef。

输出文件为csv格式的DRC违例信息,内容如下:

X,Y,DRV 0,0,0 0,1,1 0,2,0 … |

其中X,Y是tile的位置的索引,DRV为该处是否发生DRC违例,0为不发生违例,1为发生违例。

5. 评分标准

本赛题的评分主要包含两个部分,为预测精度和运行时间。测试多个隐藏案例,其中预测精度占60%,运行时间占40%。

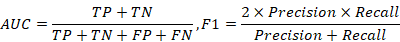

5.1 预测精度的评估指标如下:

本赛题使用准确度(AUC)和F1 score作为预测的评估指标,计算方法如下,两者各占总分30%。

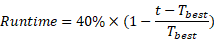

5.2 运行时间:每次预测的时间越短越好,以参赛者最快运行时间 为基准,运行时间分数计算如下:

为基准,运行时间分数计算如下:

6. 赛事组织

主办:中国计算机学会集成电路专委会

承办:CCF CHIP竞赛组委会

7. 报名与提交

报名:请点击以下链接或扫描二维码报名组委会将根据报名信息通知培训时间

https://www.wjx.top/vm/mBrTh1g.aspx

提交:请参赛队伍将作品提交至邮箱

aipc_contest@163.com

比赛设置两次提交机会,取成绩最佳的一次

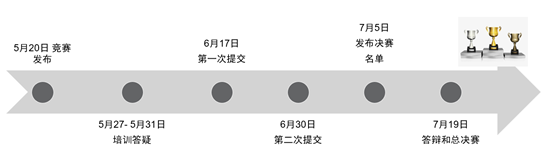

8. 比赛日程

9. 奖项与奖金

第一名 10,000元

第二名 5,000元

第三名 3,000元

优秀作品将有机会入选CCFChip大会论文集

证书:成绩前10% 一等奖证书,11- 25%, 二等奖证书,26%-40%三等奖证书

10. 比赛咨询:

aipc_contest@163.com或报名后加入群组讨论

参考资料

[1] Z. Chai, Y. Zhao, W. Liu, Y. Lin, R. Wang and R. Huang, "CircuitNet: An Open-Source Dataset for Machine Learning in VLSI CAD Applications With Improved Domain-Specific Evaluation Metric and Learning Strategies," TCAD 2023

数据集:https://circuitnet.github.io/

教程样例:https://github.com/circuitnet/CircuitNet

[2] Z. Xie et al., "RouteNet: Routability prediction for Mixed-Size Designs Using Convolutional Neural Network", ICCAD 2018.

[3] Kyeonghyeon Baek, et. al, “Pin Accessibility and Routing Congestion Aware DRC Hotspot Prediction Using Graph Neural Network and U-Net”, ICCAD 2022.

[4] AMD Ryzen™ AI 软件栈:https://ryzenai.docs.amd.com/

中国计算机学会芯片大会(CCF Chip 2024)

中国计算机学会芯片大会(CCF Chip 2024)

首页

首页